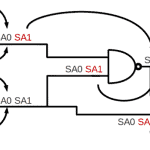

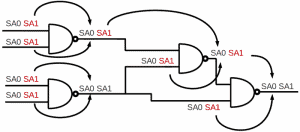

In the previous article you learned to apply the Stuck at Fault Model (S@) to a small combinational circuit.

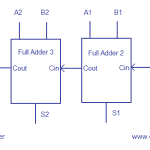

You can take the learning on the Full 1-bit adder and apply it to larger combinational circuit.

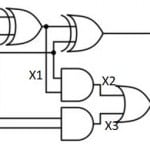

In testing lingo, you often hear people refer to this as the testing of random logic. Technically, there’s nothing random about the logic.

I think “random” gets used to contrast with the highly structured design of memory circuits into array of 1-bit cells. Memory test lends itself to algorithmic testing, for example the Marching 1. In random logic testing you may use algorithms to propagate your faults, that is automatically develop a test pattern.

You need to keep in mind that the logic being tested has a functional purpose and this can be implemented in a multitude of ways. Let’s take a second look at the adder function. [Read more…]